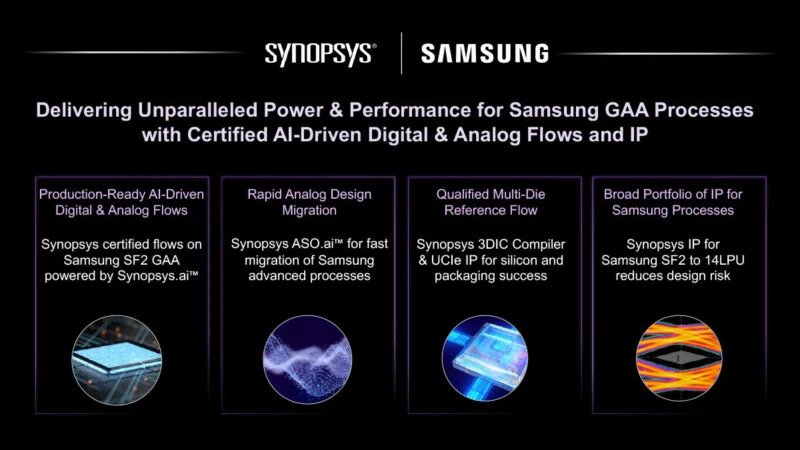

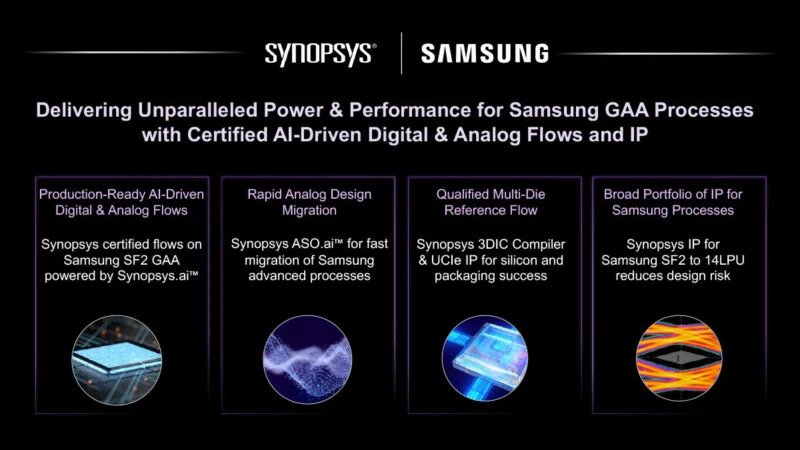

Synopsys ha annunciato che i suoi strumenti di processo di progettazione e IP sono pronti per il processo di produzione di 2 nm presso Samsung Wafer Foundries.Samsung ha recentemente annunciato che producerà in serie chip a semiconduttori di 2NM nel 2025 e ha dichiarato che il processo sarà ulteriormente migliorato nel 2027. Lo strumento di progettazione EDA di Synopsys ha superato la certificazione di processo GAA di Samsung.

Secondo l'introduzione ufficiale, il kit EDA di Synopsys può migliorare la migrazione della progettazione della simulazione, il PPA (efficienza dell'area, le prestazioni ed efficienza energetica) e la produttività dei nodi di processo GAA di Samsung Wafer Foundry.Synopsys utilizza l'intelligenza artificiale (AI) per l'ottimizzazione collaborativa per aiutare Samsung a migliorare l'efficienza dell'area, le prestazioni e l'efficienza energetica del processo di 2 nm.

Gli strumenti DSO.AI e ASO.AI di Synopsys sono stati migrati con successo da FinFET all'architettura GAA, il che significa che i clienti possono migrare senza intoppi i propri progetti di chip FinFet esistenti al nuovo processo GAA di 2NM.

Le aziende di chip possono utilizzare gli strumenti Synopsys per sviluppare nuove tecnologie di progettazione di chip, tra cui il cablaggio dell'alimentazione sul retro, i metodi di percezione dell'effetto di layout locale e la progettazione di unità di nanosheet, migliorando così l'efficienza e le prestazioni dei processi SF2.Samsung ha dichiarato che il nodo di processo SF2Z può migliorare ulteriormente le prestazioni, il consumo di energia e la densità (del 20%).

Synopsys ha anche rivelato che il suo IP UCIE è stato utilizzato nella produzione di chips presso i nodi di processo Samsung SF2 e SF4X.Inoltre, la stessa soluzione DTCO verrà utilizzata anche per ottimizzare il nodo di processo da 1,4 nm di Samsung (SF1.4).